11 月 10 日消息,Meta 和 AMD 公司在近日召开的 2023 年 OCP 峰会上,演示了 Type-3 设备的计算快速链接(CXL)内存。

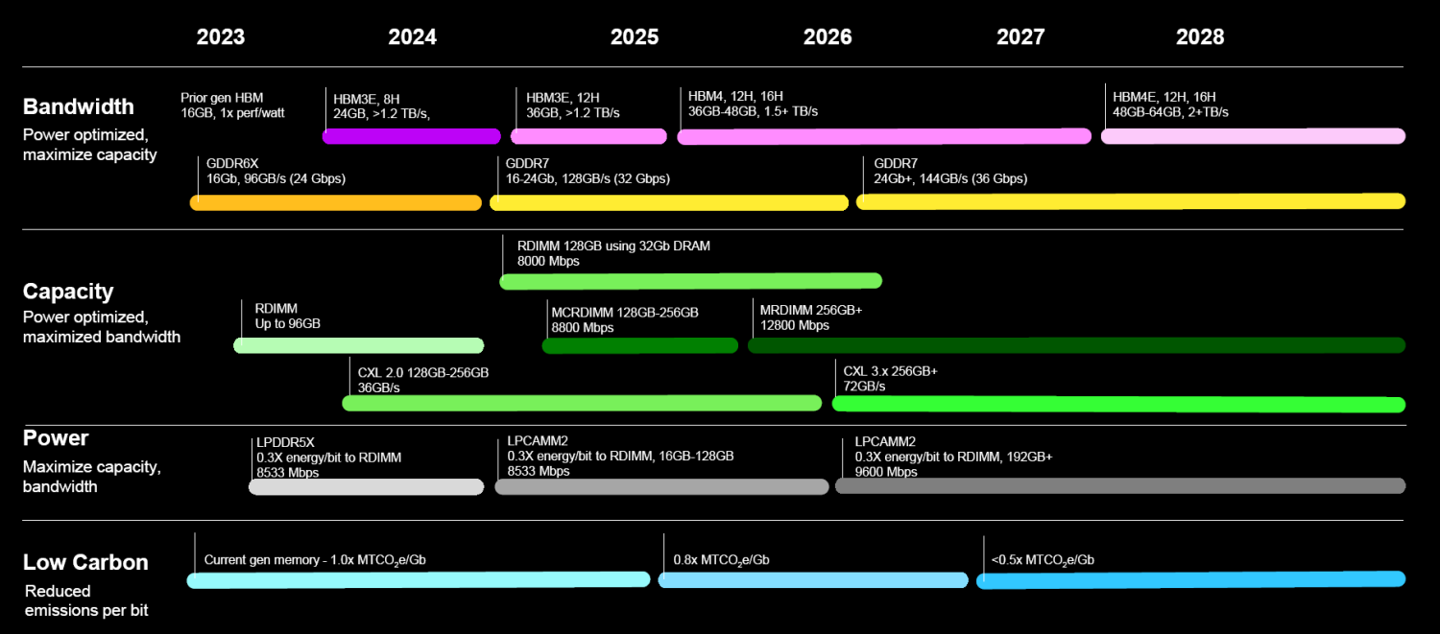

CXL 内存可以实现高速处理器到设备(processor-to-device)和处理器到内存接口(processor-to-memory interface),提高内存的使用效率,为超大规模企业节省资金,同时提高性能。

CXL 是由主要硬件供应商和云提供商于 2019 年共同制定的开放标准,目前仍在快速发展。

具体来说,与传统的 PCIe 互连相比,它提供了一组新功能,使 CPU 能够以具有加载 / 存储语义的高速缓存一致方式与外围设备(及其连接的存储器)通信。因此,与内存相关的设备扩展是 CXL 的主要目标场景之一。

CXL 标准定义了三个独立的协议:CXL.io、CXL.cache 和 CXL.mem。CXL.io 使用标准 PCIe 中的 TLP 和 DLLP 等功能,主要用于协议协商和主机设备初始化。CXL.cache 和 CXL.mem 分别为设备访问主机的内存和主机访问设备的内存使用上述协议头。

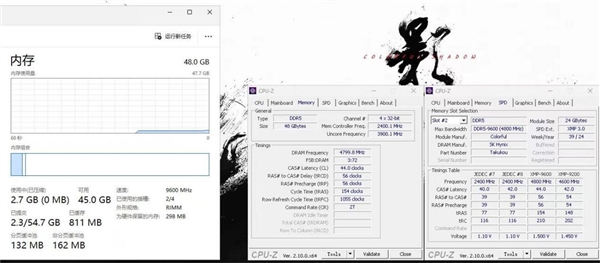

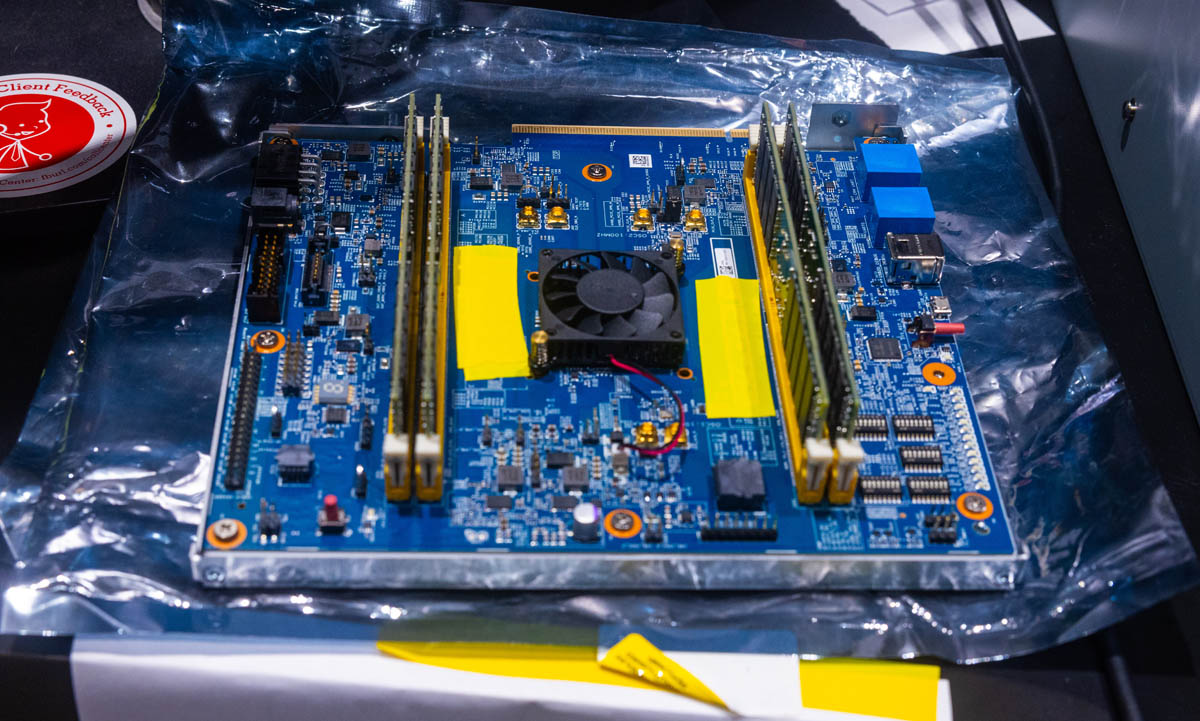

本次展示的 Type-3 设备支持 CXL.io 和 CXL.mem,并且这些设备通常被视为对现有系统的内存扩展。

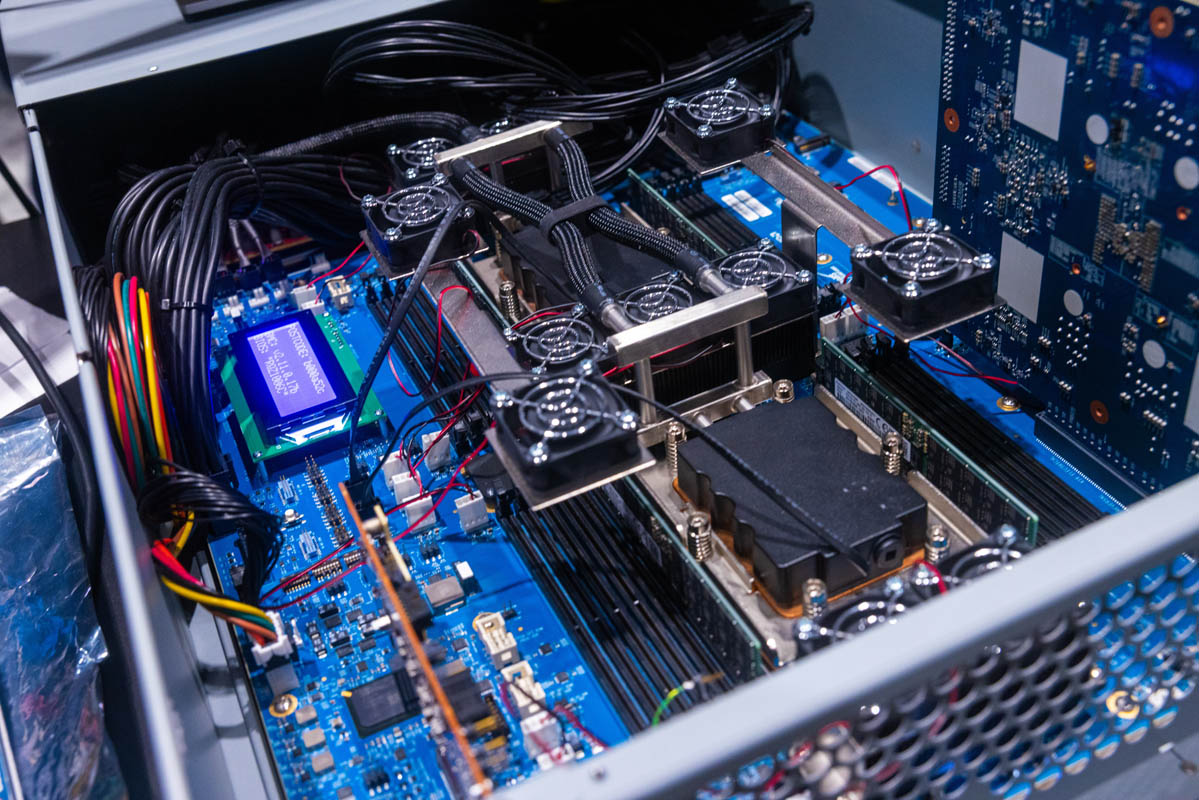

两家公司在搭载 AMD EPYC 9004 Genoa 处理器的主板上进行了演示,周围有四个双列直插式内存模块 (DIMM) 插槽,以及一个散热片和风扇,并配有 PCIe x16 连接器。

CXL 内存的主要承诺之一是它有可能让超大规模企业重用 DRAM,主控可以连接 DDR4 / DDR5 内存和 CXL,从而可能节省大量成本。

使用 CXL 内存可能是这些公司继续使用他们想要逐步淘汰的任何 DDR4 RAM 单元的一种方式,作为附加内存来增强较新的单元并增强其服务器配置。

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏