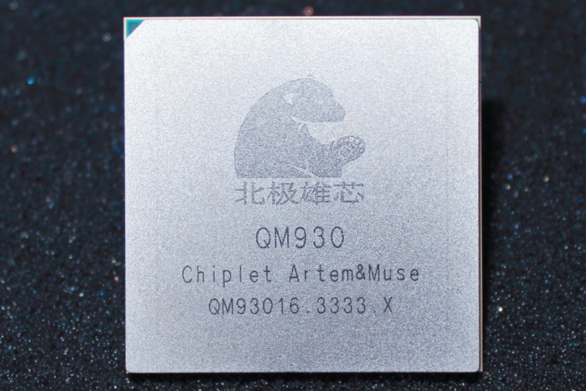

▲ 北极雄芯 256Gb / s 带宽的 D2D 测试片回片测试成功,图源北极雄芯公众号,下同

IT之家 9 月 6 日消息,近日,北极雄芯宣布自主研发的首个基于国内《芯粒互联接口标准》的 Chiplet 互联接口 PBLink 回片测试成功。PBLink 接口具备低成本、低延时、高带宽、高可靠、符合国产接口标准、兼容封装内外互连、注重国产自主可控等特点。

据介绍,该接口采用 12nm 工艺制造,每个 D2D 单元为 8 通道设计,合计提供最高 256Gb / s 的传输带宽,可采用更少的封装互连线以降低对封装的要求,最少仅需要 3 层基板进行 2D 互连。

基于专门优化的精简协议层和物理层,该接口可实现 ns 级别的端到端延迟,各项指标符合《芯粒互联接口标准》要求及设计预期。

此外,PB Link 可灵活支持封装内 Chiplet – Chiplet 互联以及 10-15cm 的封装外板级 Chip – Chip 互联,灵活适配各类下游应用场景需求。

北极雄芯表示,公司率先推出的是基于传统封装(153μm Standard Package)的芯粒解决方案,并预计在 2024~2025 年推出针对超高性能场景的高密度互连版本(55μm InFO Package)。

此外,本次回片测试成功的 PB Link 将用于公司下一代核心 HUB Chiplet 以及部分功能型 Chiplet 上,预计于 2024 年内实现整体量产。

据IT之家此前报道,北极雄芯已于今年初发布了国内首款基于 Chiplet 异构集成的人工智能计算芯片“启明 930”,中央控制芯粒采用 RISC-V CPU 核心,同时可通过高速接口搭载多个功能型芯粒,基于全国产基板材料以及 2.5D 封装。

Chiplet 架构是指通过将大芯片拆分为小芯粒进行生产并集成封装,可有效提升大算力芯片制造的综合良率,并且通过芯粒复用创造灵活性的搭配选择,目前英特尔、AMD 的产品都采用了相关技术,是传统单芯片的改进方案。

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏