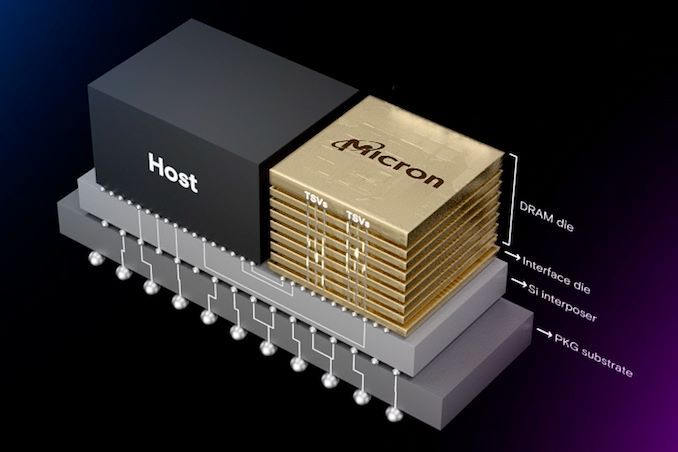

9 月 10 日消息,Rambus 公司今天(9 月 10 日)发布新闻稿,宣布推出业内首款 HBM4 内存控制器 IP,为 HBM4 内存提供各种先进的特性集,助力设计人员应对下一代 AI 加速器及图形处理单元(GPU)。

援引官方新闻稿,Rambus 公司的 HBM4 控制器 IP 不仅支持 JEDEC 规范中的 6.4 Gbps 传输速率,还能支持最高 10 Gbps 的数据传输速率,为每个内存设备提供 2.56 太字节每秒(TB/s)的数据吞吐量。

Rambus HBM4 控制器 IP 可结合第三方或客户自有的 PHY 解决方案,共同构建完整的 HBM4 内存子系统。

| HBM4 Product Brief |

HBM3E/3 Product Brief |

HBM2E/2 Product Brief |

|

|---|---|---|---|

| Speed Bins (Gb/s) | Up to 10 | Up to 9.6/8.4 | Up to 3.6/2.0 |

| Channel Densities (Gb) | Up to 32 | Up to 32 | Up to 24 |

| Channels | Pseudo-Channels | 32 | 16 | 32 | 8 | 16 |

| DRAM Stacks | Up to 16 | Up to 16 | Up to 12 |

| PHY Interface | DFI Style | DFI Style | DFI Style |

| PHY Independent Mode | Yes | Yes | Yes |

| Refresh Management Support | Yes | Yes | |

| Look-Ahead Command Processing for Minimum Latency | Yes | Yes | Yes |

| Integrated Reorder Functionality | Yes | Yes | Add-on core |

| Self-refresh and Power-down Low Power Modes |

Yes | Yes | Yes |

| RAS Features | Yes | Yes | Yes |

| Built-in Activity Monitor | Yes | Yes | Yes |

| DFI Compatible | Yes | Yes | Yes |

| End-to-end Data Parity | Yes | Yes | Yes |

| Interface to Logic | Native or AXI | Native or AXI | Native or AXI |

Rambus 高级副总裁兼总经理 Neeraj Paliwal 表示:

随着大型语言模型(LLMs)的参数规模现已超过万亿级别并持续增长,克服内存带宽和容量的瓶颈,对于满足训练和推理 AI 的实时性能要求至关重要。

我们正将业界首个 HBM4 控制器 IP 解决方案推向市场,以帮助客户在其最先进的处理器和加速器中实现突破性性能。

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏