设计芯片通常是耗时耗力的高成本工作,通常成本需要超过 1 亿美元(IT之家备注:当前约 7.31 亿元人民币),而且从概念到生产至少需要 3 年时间。而 Zero ASIC 公司希望使用无代码方式,实现芯片设计自动化。

该公司推出了 ChipMaker 平台,使用基于小芯片的设计简化了流程,隐藏了电路设计的复杂性,使用户能够在订购物理设备之前快速准确地测试和修改其定制设计。

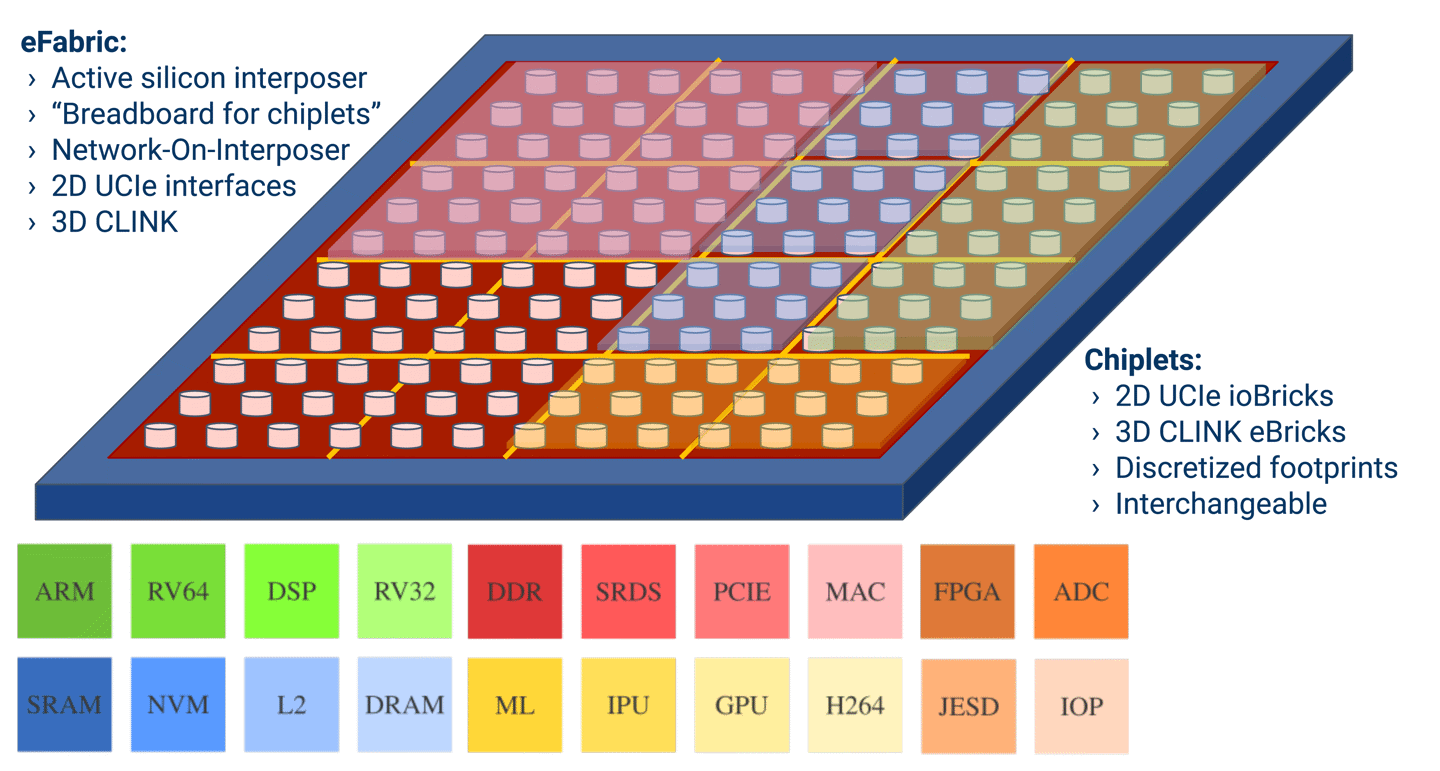

该自动化平台,主要基于 eFabric(允许芯片之间进行互连的网格状 3D 中介器)和 eBrick(一组具有即插即用功能的预制的三维芯片组),使用云现场可编程门阵列(FPGA),完成修改 RTL 源代码。

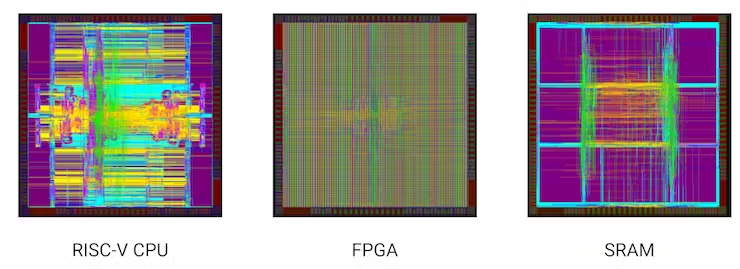

eBrick 包括支持四核 RISC-V Linux 的双核处理器、5 K LUT 嵌入式 FPGA 和 3MB SRAM-3 TOPS 机器学习加速器。

Zero ASIC 首席执行官兼创始人 Andreas Ologsson 表示:“为了打造下一波改变世界的硅器件,我们需要将 ASIC 的门槛降低几个数量级。我们 Zero ASIC 的使命是让 ASIC 的订购成为可能就像从电子产品经销商处订购目录零件一样简单。”

该公司表示,使用 ChipMaker 平台设计芯片成本只需要常规的 10 分之一或者 100 分之一,可以用于机器人、汽车安全、航空、国防以及 5G 和 6G 通信等领域。

公司表示至少要到 2024 年第 3 季度才会提供样品,所以 Nvidia 和英特尔等公司还不必担心 Zero ASIC 的产品会蚕食他们的市场份额。

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏