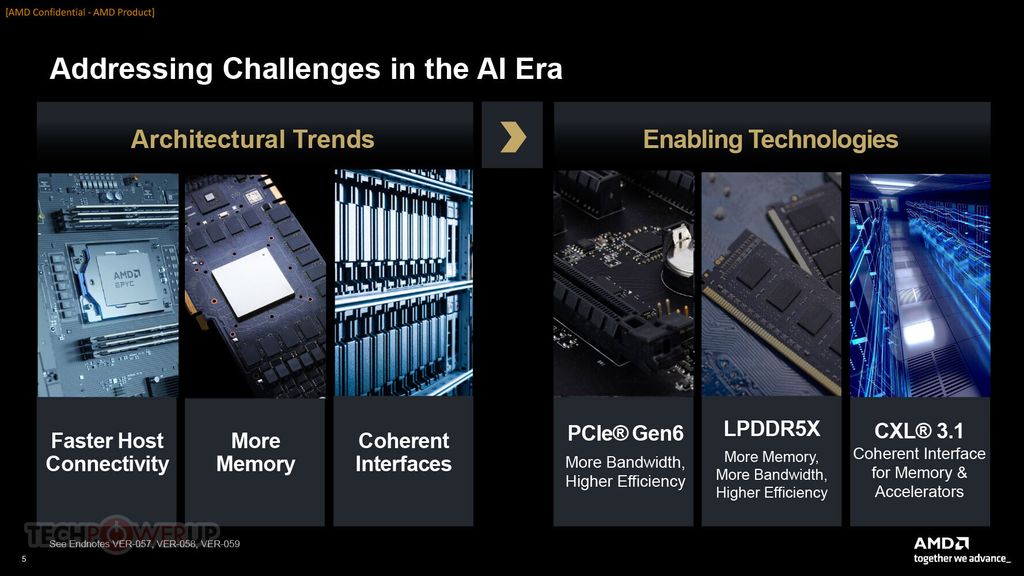

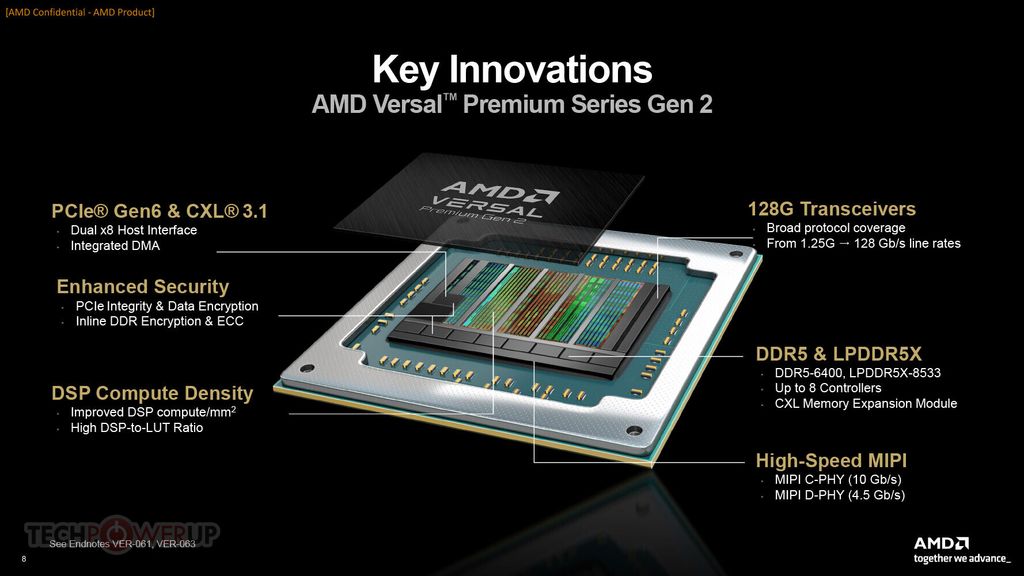

11 月 13 日消息,科技媒体 techpowerup 昨日(11 月 12 日)发布博文,报道称 AMD 宣布第二代 Versal Premium 系列自适应 SoC 平台,将成为 FPGA 行业首款在硬 IP 中采用 CXL3.1 与 PCIe Gen6 并支持 LPDDR5 存储器的器件。

高速数据访问与处理

第二代 Versal Premium 系列自适应 SoC 平台通过支持业界最快的主机接口 CXL 3.1 和 PCIe Gen 6,实现了业界领先的高带宽主机 CPU 与加速器的连接。

与支持 PCIe Gen 4 或 Gen 5 的 FPGA 相比,PCIe Gen 6 能提供 2 至 4 倍的线速率,而运行 PCIe Gen 6 的 CXL 3.1 在类似时延下则能提供使用 CXL 2.1 器件的双倍带宽,以及增强的架构和一致性功能。

提高存储器带宽及利用率

第二代 AMD Versal Premium 系列自适应 SoC 能以至高 8533 Mb/s 的最快速 LPDDR5 存储器连接加速存储器带宽,带来更快速的数据传输和实时响应。与采用 LPDDR4/5 存储器的同类器件相比,这种超快的增强型 DDR 存储器可将主机连接速度提升至高 2.7 倍。

与 CXL 存储器扩展模块进行连接可使总带宽较之单独使用 LPDDR5X 存储器高出至多 2.7 倍。

因此,第二代 Versal Premium 系列允许为多个加速器实现可扩展的内存池和扩展,进而优化存储器利用率并增加带宽和容量。

通过为多个器件动态分配内存池,第二代 Versal Premium 系列自适应 SoC 旨在提高多头单逻辑器件( MH-SLD )的存储器利用率,使其无需架构或交换机即可运行,同时支持至多两个 CXL 主机。

加强数据安全

增强的安全功能有助于第二代 Versal Premium 系列在传输和静态状态下均可快速、安全地传输数据。其是业界首款在硬 IP 中提供集成 PCIe® 完整性和数据加密( IDE )支持的 FPGA 器件 6。

CXL 3.1 和 LPDDR5X 内存的结合,有助于满足对实时处理和存储日益增长的需求。AMD 自适应与嵌入式计算集团高级副总裁 Salil Raje 表示,该平台将帮助客户提高系统吞吐量和内存资源的利用率,从而实现更高的性能。

简要介绍下本文中出现的专有名词:

现场可编程逻辑门阵列(FPGA)

FPGA(现场可编程门阵列)是一种半导体集成电路,设计者可以在现场对其逻辑电路进行编程和配置。

FPGA 允许用户在硬件层面上进行编程,能根据需要改变其功能和结构;FPGA 通常具有较低的功耗,适合于对能效有严格要求的应用场景。

CXL 3.1

Compute Express Link(CXL)是一种开放标准的高速互连技术,旨在为现代数据中心提供高效的计算和存储解决方案。

CXL 3.1 支持高达 64 GT/s 的数据传输速率,引入了可信安全协议(TSP),支持基于虚拟化的可信执行环境(TEE),以便于处理机密计算工作负载。

PCIe Gen 6

PCIe Gen 6(PCI Express 6.0)是最新发布的 PCIe 标准,传输速率达到 64 GT/s,几乎是 PCIe 5.0(32 GT/s)的两倍。

PCIe 6.0 引入了 PAM-4(脉冲幅度调制 4)技术,这种技术通过在每个信号周期内传输更多的数据位,进一步提高了数据传输效率。

PCIe 6.0 特别适合于数据中心、人工智能(AI)、机器学习(ML)和高性能计算(HPC)等领域。

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏